浙江省数据存储重点实验室建设单位杭州电子科技大学、杭州华澜微电子股份有限公司联合浪潮计算机科技有限公司、浙江大华技术股份有限公司、华中科技大学、上海交通大学等优势单位突破关键技术瓶颈,成功研制数据存储阵列芯片及系统,适配国内外主流服务器,构建起“IP- 芯片 - 系统”存储阵列产业链闭环,填补国内空白。

随着大数据、云计算和人工智能技术的飞速发展,数据已成为国家基础性、战略性的资源,数据处理(计算)、数据传输和数据存储形成了3个产业重点。我国经过几十年努力,已经布局并且形成了基本的产业链。其中,数据计算方面已经有鲲鹏、飞腾、龙芯、申威等处理器芯片,操作系统有鸿蒙、麒麟等,而在数据存储领域,主要包括存储颗粒、硬盘控制器、存储阵列控制器3个分支。闪存颗粒是存储的介质,主要由长江存储的闪存(Flash)和合肥长鑫的动态随机存储器(DRAM)担纲;单个硬盘的控制器已经有华澜微、联芸、国科微等实现了产业化;而驱动和管理多个硬盘的阵列控制芯片,因为芯片规模大、性能速度快、可靠性要求高,长期都由美国博通和微芯科技两家公司提供解决方案。

项目团队先解决了单个硬盘的控制芯片问题,研制并产业化了固态硬盘主控芯片系列,又再接再厉,十年磨一剑,打造了完整的阵列控制芯片系列,填补了国内空白。

基础IP核:基于国产工艺的高速接口IP系列产业化

海量存储系统由成千上万个硬盘组成,数据存储阵列控制器是把硬盘有效组合、搭建成为完整系统的“关节”。一方面,它要提供足够的带宽,确保服务器拥有高速数据吞吐能力,相当于“高速公路”,并管理多个硬盘组,驱动的硬盘数量越来越多,对应着存储空间越来越大;另一方面,每个硬盘的数据容量和吞吐速度也在不断提升。例如,PCIe总线已经从最初的PCIe Gen2、Gen3,升级到Gen4、Gen5,正在向Gen6推进。当前,最普及的PCIe Gen4,单通道(Lane)速度达到每秒16千兆比特;一个8通道的PCIe Gen4接口,传输速度高达每秒128千兆比特,相当于1秒钟可以传输4张DVD光盘的数据。这就需要解决高速接口的电路设计问题。

存储类芯片高速接口,最普及的类型包括SATA、SAS和PCIe,这是存储系统中不可缺少的基本接口,一般由设计公司通过从海外专业IP公司授权获得。这些高速接口的核心技术主要包括两个部分:一个是物理层(PHY)电路,核心功能是高速串并转换(SerDes), 这是高频模拟信号为主的电路;一个是协议层(Protocol)电路,主要体现在后向兼容、覆盖30多年计算机接口历史变迁的通信协议上。

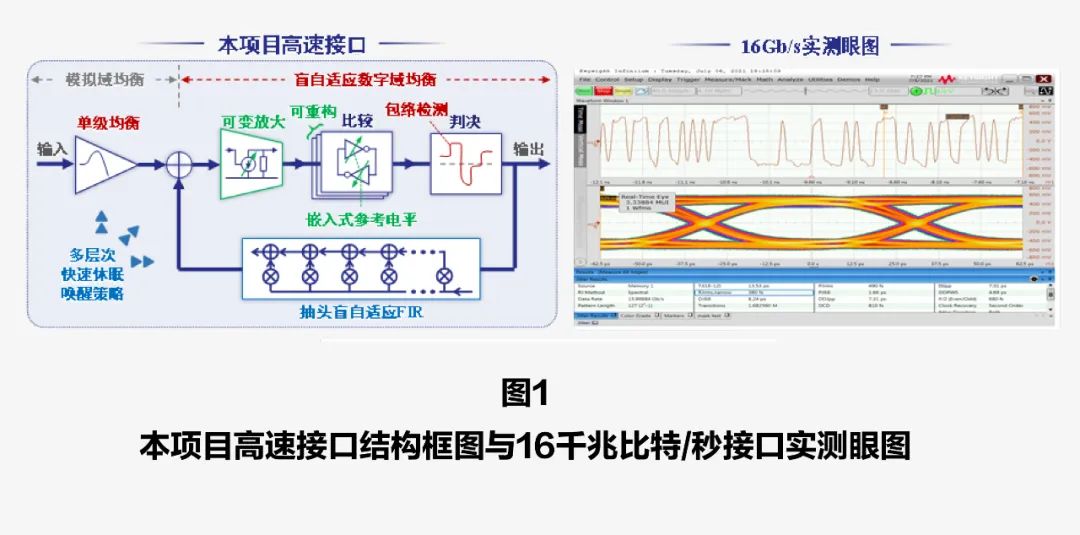

高速接口IP面临诸多挑战:数据传输速率高导致信号完整性恶化、SerDes性能下降;复杂均衡与匹配设计使功耗攀升;多级/多路并行判决电路让芯片面积增大;国产半导体工艺与国外高阶工艺存在差距,影响速度和能效。项目团队通过系统与电路架构创新,攻克SerDes核心技术:提出盲自适应校准算法与电路休眠策略,优化系统功耗;提出可重构紧凑型电路设计方法,减小链路面积;提出数字化系统架构与误差容限提升方法,补偿工艺偏差。同时,创新高速串行数据包络双电平检测及过采样方法,降低工艺复杂度和功耗。最终,基于国内成熟28纳米标准逻辑工艺,研发出SATA、SAS、PCIe等完整系列计算机接口物理层和协议层自主IP核。实测眼图表现如图1。

芯片设计:片上系统创新架构提升读写性能与数据安全

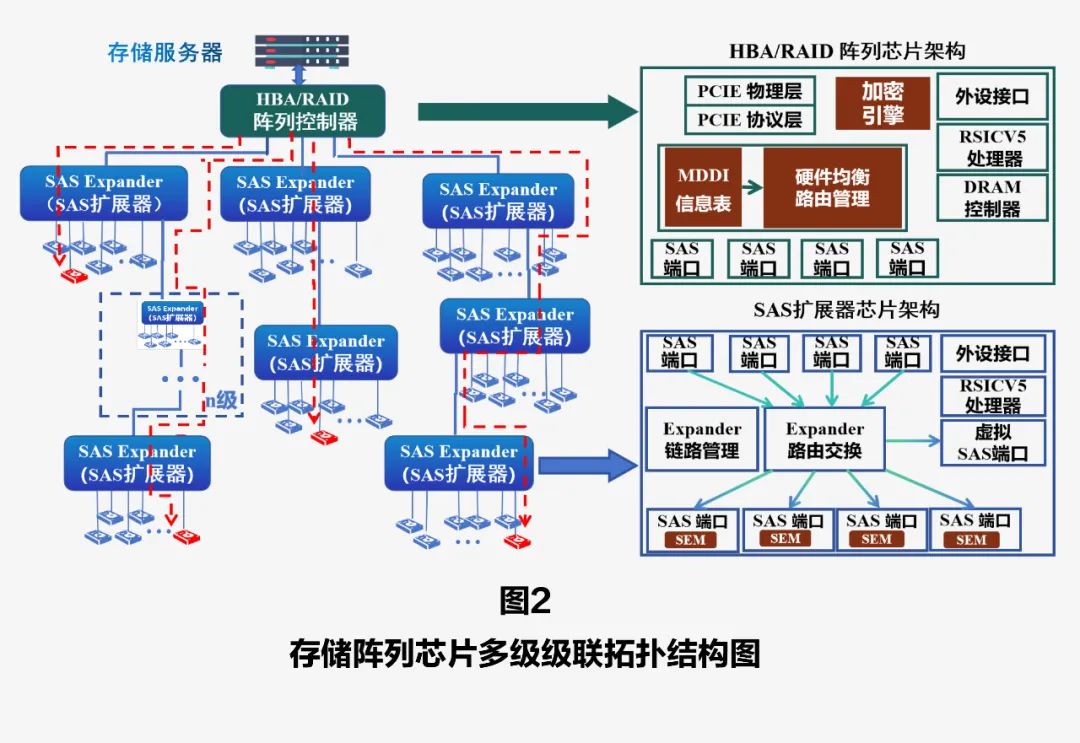

阵列控制芯片系列主要包括4个种类的型号:主机总线适配器(HBA)、冗余阵列(RAID)、扩展器(Expander)以及多端口控制器(PM)。

存储阵列控制器芯片对数据存储系统性能和安全至关重要。数据容量急剧提升,要求芯片具备强大的系统处理能力和电路架构驱动能力,实现对千百个硬盘的有效驱动和高效管理。这些芯片均为数十亿晶体管集成度的超大规模片上系统芯片(SOC),需要从基础的电路硬核模块积累,在复杂但灵活的芯片架构上运营各种存储管理和效率优化算法,提供高性能、大容量、高可靠性的海量数据存储系统。

项目团队创新性地提出基于复杂拓扑结构下传输节点和存储节点的多维度动态管理阵列芯片架构(如图2所示),涵盖拓扑结构路由表(级联深度,访问路径)、传输节点动态信息表(节点带宽、节点任务)、硬盘动态信息表(硬盘响应时间、队列深度、实时读写性能)等多维参数,感知硬件特性并优化链路,降低系统性能波动,提升读写性能。

存储系统:软硬协同高效数据存储方法

全闪存阵列存储普及下,固态硬盘特性带来大量重复数据(比如存储阵列主存储有42%~68%的重复数据,备份存储中有69%~97%的重复数据),传统数据去重技术面临挑战。主机与SSD双层地址映射导致冗余浪费及元数据I/O放大(4.4~27.3倍);单设备重删技术在阵列系统中丢失跨盘重删机会(丢失70%跨盘重删机会)。同时,国产CPU性能与主流CPU存在差距,成为存储瓶颈,需软硬件协同解决。

项目团队提出软硬件协同低开销重删ARM-Dedup算法,重构SSD固件层实现阵列级地址映射管理,结合版本化指纹验证保障数据一致性,跨盘重复数据删除效果显著。针对低开销下随机I/O性能问题,提出智能路径管理算法,加速追加写随机I/O模型,提升随机小块数据读写性能,有效突破了存储阵列性能瓶颈。

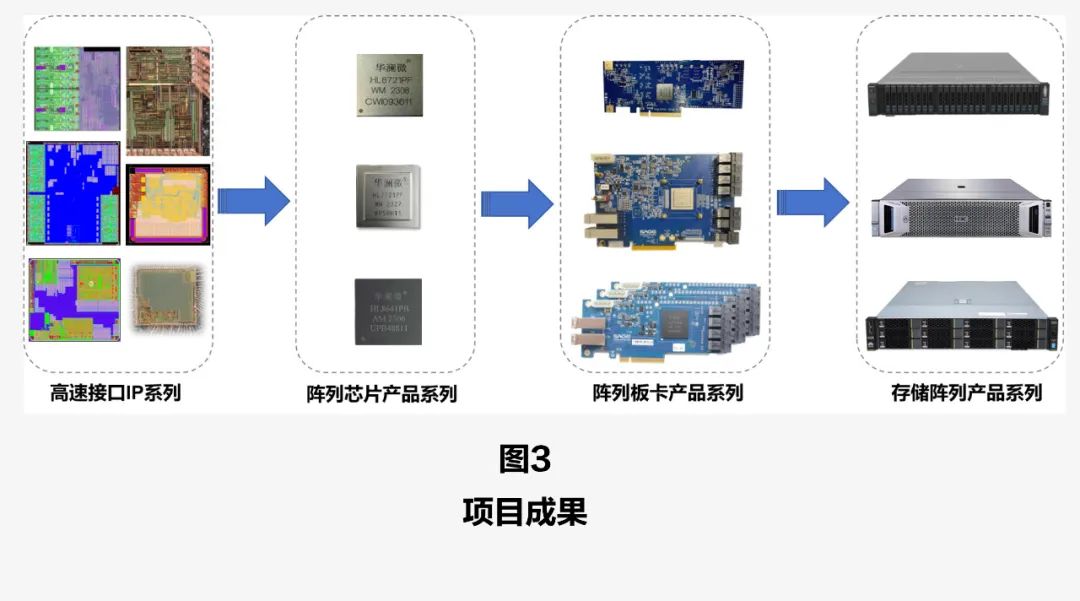

数据存储阵列核心芯片研发和产业化项目成功实现了从高速接口IP到存储阵列控制芯片,再到软硬协同存储方法的技术创新。如图3所示,这些创新成果被国内头部存储系统厂家迅速应用,为数据产业的蓬勃发展筑牢了坚实的芯片级硬核技术基础。项目所积累的技术经验和创新成果将为全球存储技术的发展注入新的动力,持续贡献来自中国的智慧和力量,推动全球存储产业向更高效、更可靠的方向迈进。

致谢:感谢国家重点研发计划项目(2018YFB2202900)、国家自然科学基金项目(U1709220)、浙江省尖兵领雁项目(2024C01001)的支持。